中古 TEL / TOKYO ELECTRON ACT 12 #9364744 を販売中

URL がコピーされました!

タップしてズーム

ID: 9364744

ウェーハサイズ: 12"

ヴィンテージ: 2004

(4) Coater / (4) Developer system, 12"

Wafer type: Notch

Right to left

Loading configuration: (3) Uni cassettes

Cassette type: FOUP

Inline

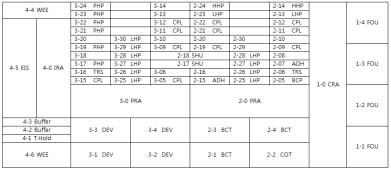

CSB

PRB1

PRB2

IFB

AC Power box

(2) Chemical boxes

Main controller

25-Slots

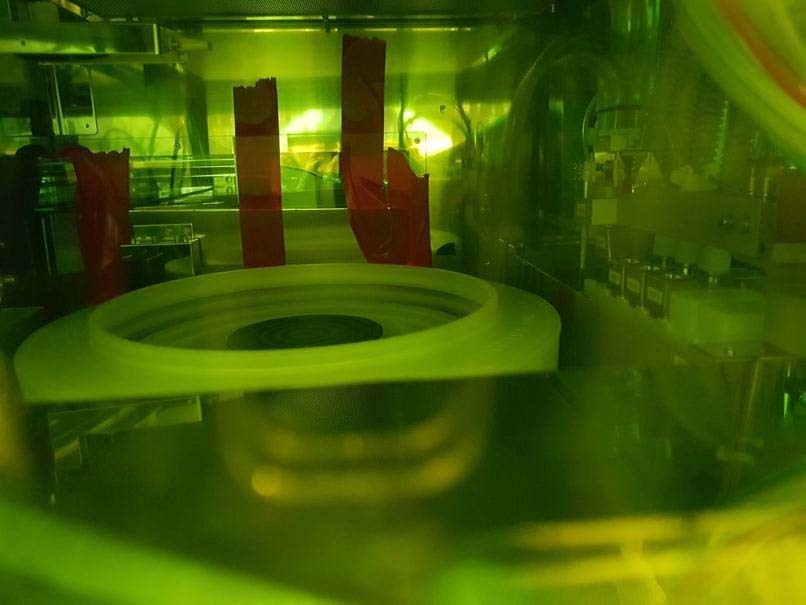

Coater unit (2-1, 2-2 Modules):

(4) Dispense nozzles with temperature controller lines

RDS Pump

PR Suck-back valve: (8) Auto suck-back valves

Manual drain

Programmable side rinse: CCSS Thinner supply

BCT Unit (2-3,2-4 Modules):

(2) Dispense nozzles with temperature controller line

RDS Pump

PR Suck-back valve: (4) Auto suck-back valves

Rinse system: 3-Liters (2) buffer tank systems

Manual drain

Programmable side rinse:

Thinner supply: CCSS

Developer unit (3-1, 3-2, 3-3, 3-4 Modules):

NLD Nozzle / Unit

(2) Stream nozzles for DI rinse

2-Points for back side rinse

Developer system: 3-Liter (2) buffer tank systems

Developer supply: CCSS

Developer temperature controller

Direct drain

ASML I/F Wafer stage

Temperature Control Unit (TCU)

(2) Chemical cabinets

T and H Controller missing

Power supply: AC 208 V, 3 Phase

2004 vintage.

TEL/TOKYO ELECTRON ACT 12フォトレジスト装置は、半導体デバイス製造のリーディングシステムの1つです。このシステムは、CPU、 GPU、メモリなどの半導体デバイスの製造に使用される薄膜の開発と製造のために設計されています。高度なデバイス統合に必要な精密な薄膜処理を提供し、薄膜形成を微調整する高性能機能を備えています。TEL ACT 12ユニットには、フォトレジストパターニング用の強力な電子ビームと、薄膜の正確な位置決めとパターニングのための高精度露光ステージが装備されています。独自のデュアルビームマッピングマシン(DBMS)を使用することで、薄膜形成において高いレベルの均一性と精度を提供することができます。DBMSは、試料の全領域にわたる電子ビーム線量分布を同時に検出して解析することができ、薄膜パターンの高分解能ビューを提供します。また、パターン生成を最適化するための高精度なステージと複数のパターニングアルゴリズム、露光条件を監視・診断する強力なソフトウェアを備えた東京エレクトロンACT12。このアセットは、多様なフォトレジスト材料をサポートし、複雑な構造の異なるパターンの処理を可能にします。このモデルは、熱制御、多軸アライメント、部品保護など、さまざまなオプションにも対応しています。高精度、高性能、高度な機能を兼ね備えたACT12フォトレジスト装置は、ハイエンドの半導体デバイス製造に最適なソリューションです。このシステムは、最高レベルの性能と精度を提供し、デバイスメーカーが市場で最も高品質で最先端の半導体デバイスを製造することを可能にします。また、所有コストが極めて低く、あらゆる生産環境に最適です。

まだレビューはありません