中古 TEL / TOKYO ELECTRON ACT 12 #9112086 を販売中

URL がコピーされました!

タップしてズーム

ID: 9112086

Driver control assembly, P/N: MSD261Y81

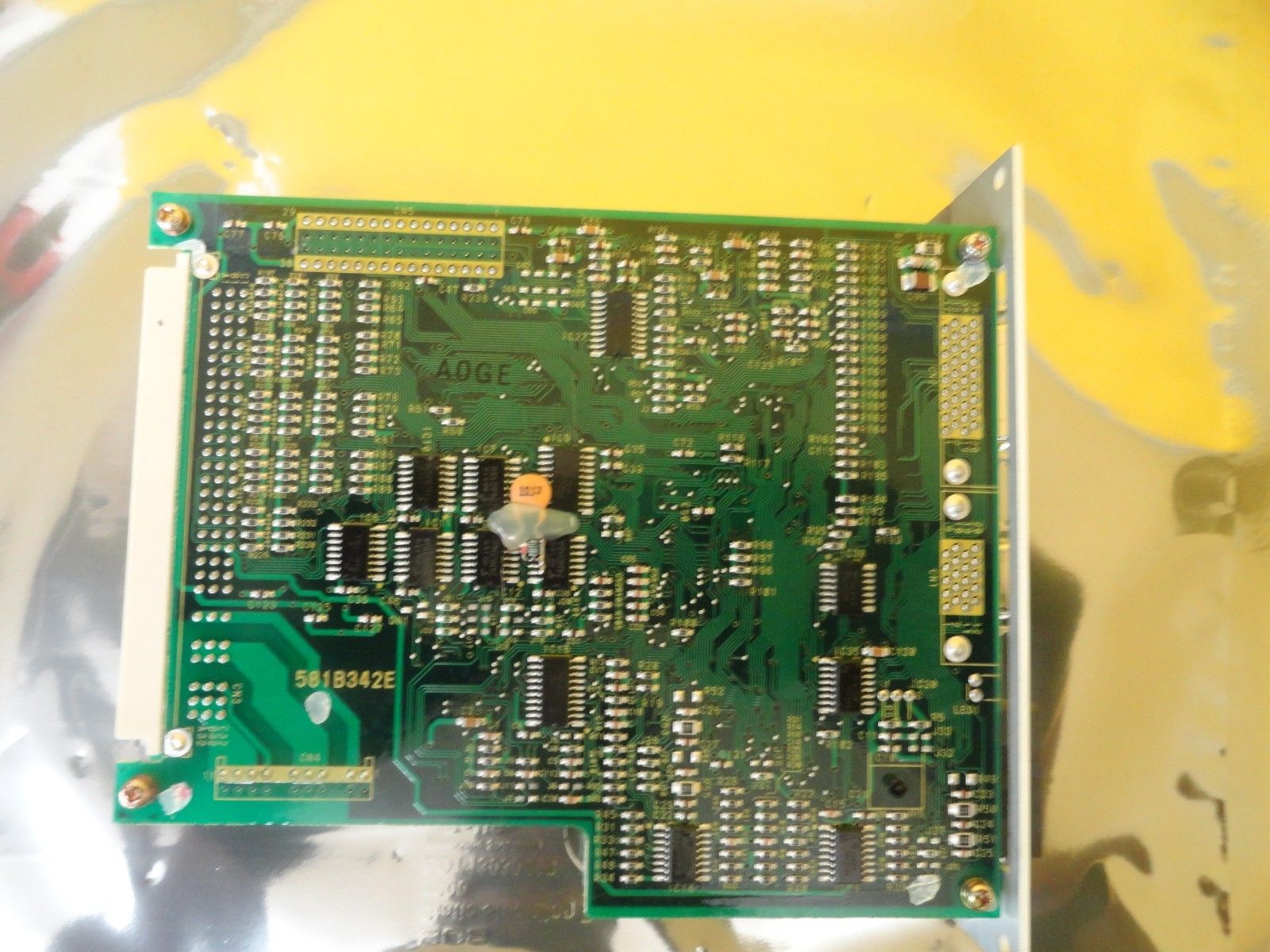

Installed PCB Cards:

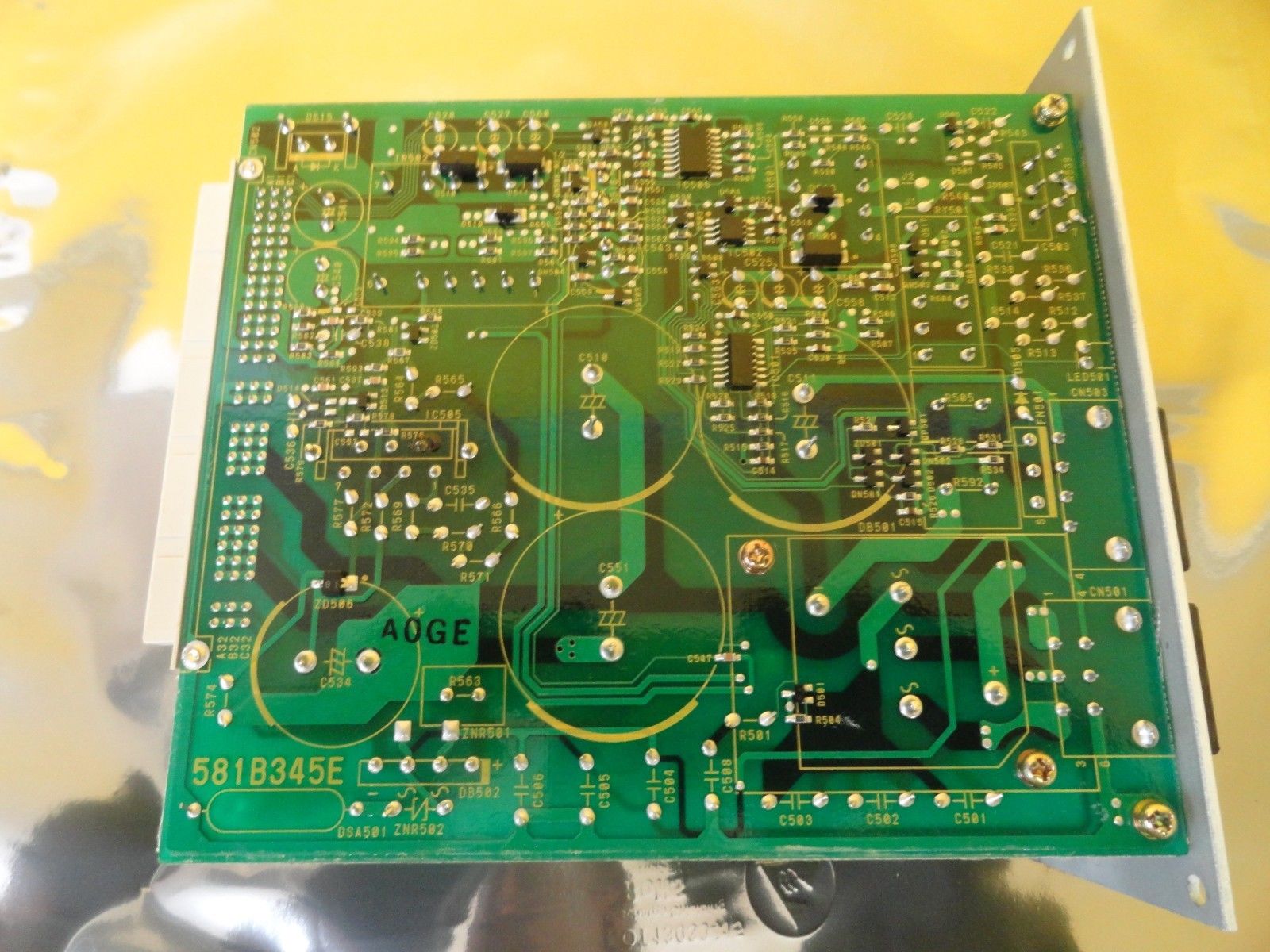

Power Supply PCB, P/N: 581B345E

Communication PCB, P/N: 581B357C

Driver Unit PCB, P/N: MSD043A1Y03

X1 Driver Unit PCB, P/N: MSD3AZA1Y04

X2 Driver Unit PCB, P/N: MSD3AZA1Y04

X3 Driver Unit PCB, P/N: MSD3AZA1Y04.

TEL/TOKYO ELECTRON ACT 12フォトレジスト装置は、高度な半導体デバイス製造のパターン処理に使用されるリソグラフィーシステムです。薄膜レジストを正確に適用するための高度なフォトレジストスピンコーティングプロセスと、高度な半導体チップ上のパターン層への高精度な露出を提供します。スピン速度7,000rpm,基板温度300°Cまでの同時スピンコーティングが可能です。TEL ACT 12は、UVから深紫外線まで幅広い露光波長のフォトレジストを使用でき、EBRモードを使用して1時間で最大4500ウェハデータセットを提供できます。TOKYO ELECTRON ACT12は、コートに使用されるレジストをマッチさせ、プロセスを露出させる高解像度ズームマッピングマシンを搭載し、ウェーハ表面全体にわたって均一なウェーハ厚と高画質を維持します。このズームマッピング機能は、高度なスピンコーティング位置規則(SCPR)の結果としてレジスト厚さを非常に正確に制御することができます。SCPRツールを使用すると、ウェーハ上のフォトレジスト位置を高精度にプリセットすることができ、スピンコート工程中の均一な膜厚の均一性が保証されます。ACT 12フォトレジスト資産には、ウェーハ上の非常に薄いフィルム層をエッチングするために使用できる高度な反応イオンエッチング(RIE)も装備されています。RIEはプラズマベースのエッチングプロセスで、高度な半導体ウェーハの表面特性のパターニングと制御に優れた精度を提供します。非常に薄い表面層を実現し、小さな特徴をパターン化し、2次元または3次元の特徴を正確に制御するために使用できます。RIEを使用して、アスペクト比が1:2以上、線幅が0。35umのエピコンパチブル構造(デバイス)を生成することができます。このモデルはまた、フォトレジスト操作のパフォーマンスを正確に制御する機能を提供する組み込みソフトウェアを備えた高度なアノテーション機能を備えています。それはまた装置の性能を微調整するのに使用することができるパターンの高度の注釈を可能にします。また、パターニングの高速化とリアルタイム欠陥検査に役立つ自動アライナーも備えています。TEL/TOKYO ELECTRON ACT12フォトレジストユニットは、半導体デバイス向けの高度なパターニングプロセスの製造における最高の要件を満たすように設計されています。その機能により、高精度のコートと露出プロセス、高解像度ズームマッピング、高速RIEエッチング、高度なアノテーション機能を提供することができます。この高度なツールは、高性能で信頼性の高いデバイスの生産を確実にするのに役立ちます。

まだレビューはありません