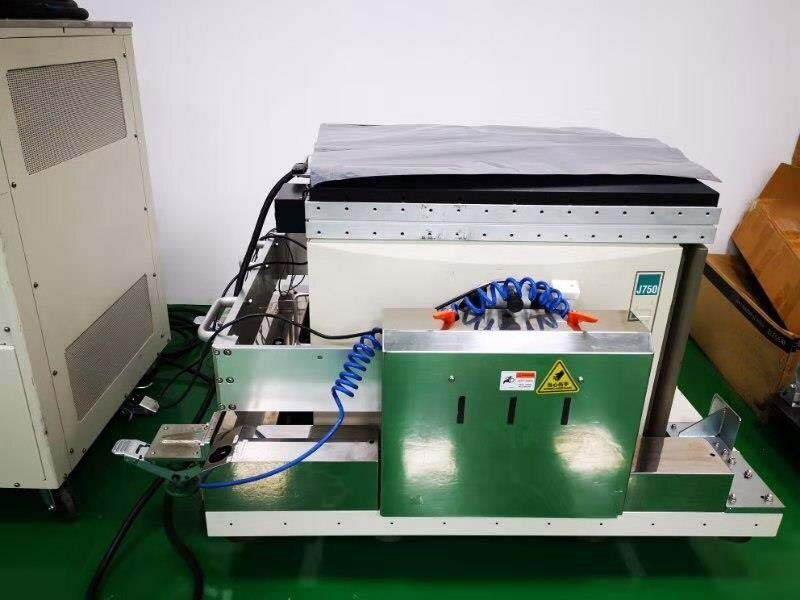

中古 TERADYNE J750 #9314722 を販売中

URL がコピーされました!

タップしてズーム

ID: 9314722

ヴィンテージ: 2001

Tester

Test head frame: 512

64 Pin / Channel card

(8) Cards

512 Channels

LVM 16 M

Date rate: 100 MHz

Edge placement accuracy: ± 500 Ps

(2) DPS (8 Channels / board)

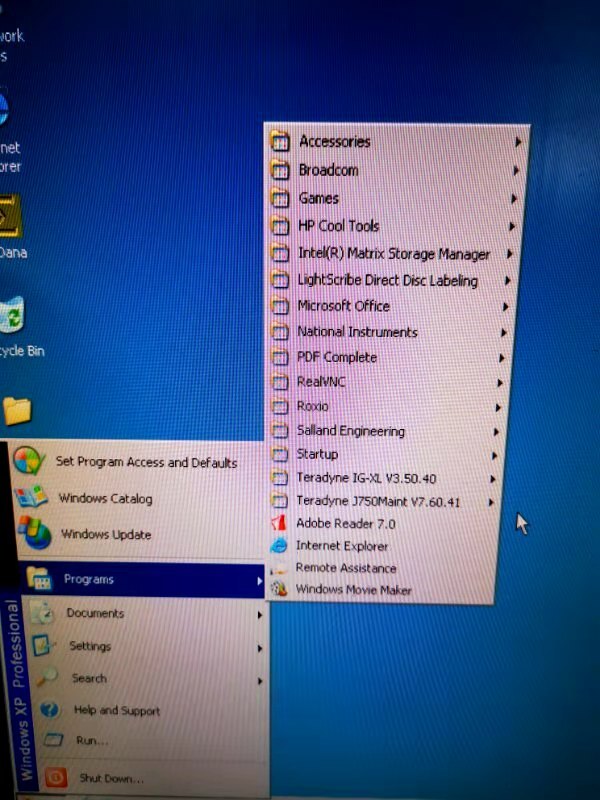

IGXL: 3.40.13

Workstation: Pentium-Xeon

Computer: XW8400 / Z800

Tester and handler communication: DIO Handler

With I/F board PCIT (918-338-20)

YAC Manipulator

2001 vintage.

TERADYNE J750 Final Test Equipmentは、半導体デバイス、デジタル集積回路、デジタル信号プロセッサなど、さまざまなコンポーネントの正確で信頼性の高いデータを提供する高速で高効率の試験システムです。自動車、消費者、産業用途など、幅広いエレクトロニクスのテストに最適です。TERADYNE J 750は堅牢でモジュラーアーキテクチャに基づいて構築されており、正確で再現性の高いテスト結果を実現します。これは、高速、低電圧プロービング、およびデュアルチャネルLVDS機能を備えた最大2,500テストポイントのテスト容量を備えています。このユニットは、複数の電源レベル、信号経路、およびビデオ信号をサポートしているため、さまざまなコンポーネントに適しています。その汎用性の高いテストアーキテクチャは、効率的な機械構成と高速デバッグアルゴリズムをサポートし、テストプロセスを高速化します。J750は精密なテスト機能を備えており、コンポーネントがターゲットアプリケーションで正しく動作することをしっかりと制御し、信頼できるようにします。これは、JEDEC、 CE、 ISOなどの規格を満たさなければならない自動車や航空宇宙部品などの高信頼性アプリケーションにとって特に重要です。J 750は、ロジック、タイミング、信号整合性、消費電力など、コンポーネントのすべての要素をテストできます。このツールは、テスト開発とデバッグプロセスを合理化するための強力な開発およびデバッグツールによってもサポートされています。これらには、コンポーネント固有の堅牢なテストを作成するプロセスを簡素化する統合テストジェネレータが含まれます。また、コンパイラとアセンブラも含まれており、カスタムテストアルゴリズム用のプログラムを書くことができ、開発者は低レベルのテストプログラムを作成することができます。TERADYNE J750は動的リンクライブラリのサポートも提供しており、テストリソースを標準化されたライブラリコンポーネントに組み合わせることができます。また、TERADYNE J 750は、試験結果へのアクセスと管理を容易にし、グラフィカルレポートとして見ることができます。レポート形式により、データを迅速に分析し、結果に基づいて行動することができます。また、すべてのテストと結果を追跡、検証、アーカイブできるようにトレーサビリティを提供します。全体的J750、 Final Test Assetはさまざまなテストおよび検証目的に適しています。正確で繰り返し可能なテスト、強力な開発とデバッグツール、信頼性の高いテスト結果により、さまざまな業界のコンポーネントをテストするのに理想的なソリューションです。

まだレビューはありません